# ne<mark>x</mark>peria

#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <u>http://www.nxp.com</u>, <u>http://www.philips.com/</u> or <u>http://www.semiconductors.philips.com/</u>, use <u>http://www.nexperia.com</u>

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use **salesaddresses@nexperia.com** (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

# AN11733 Logic data sheet parameters Rev. 2 — 15 October 2015

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Abstract | NXP's standard-logic products data sheets describe the device function,<br>and provide electrical and mechanical specifications including available<br>package types and footprints. These specifications include acronyms,<br>numerical limits, test conditions and data that can be confusing at times<br>for the user to understand. In order to correctly use these devices in a<br>system design and to build robust products, it is critical to fully understand<br>and interpret their specifications and parameters. This application<br>note explains logic device parameters such as absolute maximum,<br>recommended operating conditions, static and dynamic characteristics,<br>timing and noise characteristics, etc., as specified in the data sheets. With<br>the data sheet parameters clearly explained, system designers can use<br>the logic devices within NXP's recommended specifications and ensure<br>maximum system reliability. |

#### **Revision history**

| Rev  | Date     | Description      |

|------|----------|------------------|

| v.1  | 20150923 | Draft version.   |

| v. 2 | 20151015 | Release version. |

## **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN11733

All information provided in this document is subject to legal disclaimers.

**Application note**

# 1. Electrical characteristics

#### 1.1 Currents

Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device.

$I_{CC}$  /  $I_{DD}$  (supply current): the current flowing into the V<sub>CC</sub> / V<sub>DD</sub> supply terminal.

$\Delta I_{CC}$  (additional supply current): the increase in supply current per input pin at the specified input voltage and V<sub>CC</sub>.

**I**<sub>GND</sub> (ground current): the current flowing into the GND terminal.

${\bf I}_{\rm I}$  (input leakage current): the current flowing into a device at a specified input voltage and V  $_{\rm CC}$

IIK (input diode current): the current flowing into a device at a specified input voltage.

I<sub>O</sub> (output current): the current flowing into a device at a specified output voltage.

$I_{OFF}$  (power-off leakage current): the current flowing into a device at a specified voltage when  $V_{CC} = 0$  V.

$I_{OZ}$  (OFF-state output current): the current flowing into a 3-state output in the OFF-state at a specified output voltage and V<sub>CC</sub>.

$I_{OH}$  (HIGH-level output current): the current flowing into an output that is driving HIGH at a specified output voltage and V<sub>CC</sub>.

$I_{OL}$  (LOW-level output current): the current flowing into an output that is driving LOW at a specified output voltage and V<sub>CC</sub>.

${\rm I_{BHL}}$  (bus hold LOW current): the current flowing into a bus hold input set LOW at a specified input voltage and  ${\rm V_{CC}}.$

${\bf I_{BHH}}$  (bus hold HIGH current): the current flowing into a bus hold input set HIGH at a specified input voltage and  $V_{\rm CC}.$

$I_{BHLO}$  (bus hold LOW overdrive current): the current required to switch a bus hold input from a LOW to HIGH at a specified V<sub>CC</sub>.

${\bf I}_{\rm BHHO}$  (bus hold HIGH overdrive current): the current required to switch a bus hold input from a HIGH to LOW at a specified V\_{CC}.

$I_{O(pu/pd)}$  (power-up/power-down output current): the current flowing into an output during power-up or power-down at a specified output voltage and V<sub>CC</sub>.

#### 1.2 Voltages

All voltages are referenced to GND or  $V_{SS}$ , the most negative potential applied to the device.

**GND / V<sub>SS</sub> (supply voltage)**: for a device with a single negative power supply, the most negative power supply. Used as the reference level for other voltages; typically ground.

V<sub>CC</sub> / V<sub>DD</sub> (supply voltage): the most positive potential on the device.

$V_{EE}$  (supply voltage): one of two (GND and  $V_{EE}$ ) negative power supplies. For a device with dual negative power supply, the most negative power supply.

V<sub>I</sub> (input voltage): the range of voltages that can be applied to an input pin.

V<sub>o</sub> (output voltage): the range of voltages that can be applied to an output pin.

**V<sub>IH</sub> (HIGH-level input voltage)**: the range of input voltages that represents a logic HIGH level in the system.

**V<sub>IL</sub> (LOW-level input voltage)**: the range of input voltages that represents a logic LOW level in the system.

**V<sub>OH</sub> (HIGH-level output voltage)**: the range of voltages at an output terminal with a specified output loading and supply voltage. Device inputs are conditioned to establish a HIGH level at the output.

V<sub>OL</sub> (LOW-level output voltage): the range of voltages at an output terminal with a specified output loading and supply voltage. Device inputs are conditioned to establish a LOW level at the output.

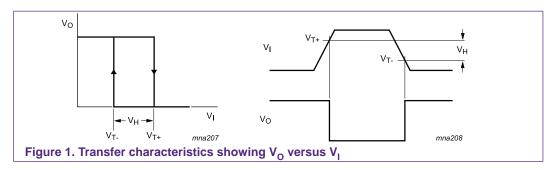

**V<sub>T+</sub> (positive-going threshold)**: the input voltage threshold that represents a logic HIGH level in the system.

$V_{T-}$  (negative-going threshold): the input voltage threshold that represents a logic LOW level in the system.

V<sub>H</sub> (hysteresis): the difference between the positive-going and negative-going thresholds.

Built in DC hysteresis in logic devices is useful in systems where inputs have some noise due to electromagnetic induction, or cross talk etc. Each input has immunity against noise depending on the amount of hysteresis voltage present.

AN11733

# 2. Typical data sheet view

#### 9. Recommended operating conditions

| Table 6.              | Recommended operating conditions    |                                                    |      |     |                 |      |  |

|-----------------------|-------------------------------------|----------------------------------------------------|------|-----|-----------------|------|--|

| Symbol                | Parameter                           | Conditions                                         | Min  | Тур | Max             | Unit |  |

| V <sub>CC</sub>       | supply voltage                      |                                                    | 1.65 | -   | 5.5             | V    |  |

| VI                    | input voltage                       |                                                    | 0    | -   | 5.5             | V    |  |

| Vo                    | output voltage                      | Active mode                                        | 0    | -   | V <sub>CC</sub> | V    |  |

|                       |                                     | $V_{CC} = 0 V$ ; Power-down mode                   | 0    | -   | 5.5             | V    |  |

| T <sub>amb</sub>      | ambient temperature                 |                                                    | -40  | -   | +125            | ۰C   |  |

| $\Delta t / \Delta V$ | input transition rise and fall rate | $V_{CC}$ = 1.65 V to 2.7 V                         | -    | -   | 20              | ns/V |  |

|                       |                                     | $V_{CC} = 2.7 \text{ V} \text{ to } 5.5 \text{ V}$ | -    | -   | 10              | ns/V |  |

#### **10. Static characteristics**

Table 7.

Static characteristics

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| Symbol                             | Parameter                   | Conditions                                                                            | - 40                  | – 40 °C to +85 °C |              |                       | • +125 ⁰C    | Unit |

|------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|-----------------------|-------------------|--------------|-----------------------|--------------|------|

|                                    |                             |                                                                                       | Min                   | Typ[1]            | Max          | Min                   | Max          |      |

| V <sub>IH</sub>                    | HIGH-level<br>input voltage | V <sub>CC</sub> = 1.65 V to 1.95 V                                                    | 0.65V <sub>CC</sub>   | -                 | -            | $0.65V_{CC}$          | -            | V    |

|                                    |                             | $V_{CC}$ = 2.3 V to 2.7 V                                                             | 1.7                   | -                 | -            | 1.7                   | -            | V    |

|                                    |                             | $V_{CC}$ = 2.7 V to 3.6 V                                                             | 2.0                   | -                 | -            | 2.0                   | -            | V    |

|                                    |                             | $V_{CC}$ = 4.5 V to 5.5 V                                                             | $0.7V_{CC}$           | -                 | -            | $0.7V_{CC}$           | -            | V    |

| V <sub>IL</sub><br>V <sub>OH</sub> | LOW-level                   | $V_{CC}$ = 1.65 V to 1.95 V                                                           | -                     | -                 | $0.35V_{CC}$ | -                     | $0.35V_{CC}$ | V    |

|                                    | input voltage               | $V_{CC}$ = 2.3 V to 2.7 V                                                             | -                     | -                 | 0.7          | -                     | 0.7          | V    |

|                                    |                             | $V_{CC}$ = 2.7 V to 3.6 V                                                             | -                     | -                 | 0.8          | -                     | 0.8          | V    |

|                                    |                             | $V_{CC}$ = 4.5 V to 5.5 V                                                             | -                     | -                 | $0.3V_{CC}$  | -                     | $0.3V_{CC}$  | V    |

| V <sub>OH</sub>                    | HIGH-level                  | $V_{I} = V_{IH} \text{ or } V_{IL}$                                                   |                       |                   |              |                       |              |      |

|                                    | output voltage              | $I_{O} = -100 \ \mu A;$<br>$V_{CC} = 1.65 \ V \ to \ 5.5 \ V$                         | V <sub>CC</sub> - 0.1 | -                 | -            | V <sub>CC</sub> - 0.1 | -            | V    |

|                                    |                             | $I_{O} = -4 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                      | 1.2                   | -                 | -            | 0.95                  | -            | V    |

|                                    |                             | $I_O = -8$ mA; $V_{CC} = 2.3$ V                                                       | 1.9                   | -                 | -            | 1.7                   | -            | V    |

|                                    |                             | $I_0 = -12 \text{ mA}; V_{CC} = 2.7 \text{ V}$                                        | 2.2                   | -                 | -            | 1.9                   | -            | V    |

|                                    |                             | $I_0 = -24$ mA; $V_{CC} = 3.0$ V                                                      | 2.3                   | -                 | -            | 2.0                   | -            | V    |

|                                    |                             | $I_0 = -32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                        | 3.8                   | -                 | -            | 3.4                   | -            | V    |

| V <sub>OL</sub>                    | LOW-level<br>output voltage | $V_{I} = V_{IH} \text{ or } V_{IL}$                                                   |                       |                   |              |                       |              |      |

|                                    |                             | $I_{O} = 100 \ \mu\text{A};$<br>$V_{CC} = 1.65 \ \text{V} \text{ to } 5.5 \ \text{V}$ | -                     | -                 | 0.1          | -                     | 0.1          | V    |

|                                    |                             | I <sub>O</sub> = 4 mA; V <sub>CC</sub> = 1.65 V                                       | -                     | -                 | 0.45         | -                     | 0.70         | V    |

|                                    |                             | $I_{O} = 8 \text{ mA}; V_{CC} = 2.3 \text{ V}$                                        | -                     | -                 | 0.3          | -                     | 0.45         | V    |

|                                    |                             | $I_0$ = 12 mA; $V_{CC}$ = 2.7 V                                                       | -                     | -                 | 0.4          | -                     | 0.60         | V    |

|                                    |                             | $I_0 = 24 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                         | -                     | -                 | 0.55         | -                     | 0.80         | V    |

|                                    |                             | $I_0 = 32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                         | -                     | -                 | 0.55         | -                     | 0.80         | V    |

# 3. Analog switches

$R_{ON}$  (ON resistance): the effective ON state resistance of an analog switch, at a specified voltage across the switch, output load and  $V_{CC}$ .

R<sub>ON(peak)</sub> (ON resistance (peak)): the maximum ON state resistance of an analog switch, over the allowed input voltage range.

**R**<sub>ON(rail)</sub> (ON resistance (rail)): the ON state resistance of an analog switch, at an input voltage equal to supply voltage or ground.

$\Delta R_{ON}$  (ON resistance mismatch between channels): the difference in ON resistance between any two analog switches within a device.

**R<sub>ON</sub>(flat) (ON resistance (flatness))**: the difference in ON resistance of an analog switch over the allowed input voltage range.

C<sub>S(ON)</sub> (ON-state capacitance): the internal capacitance seen at an analog switch terminal when the switch is closed or ON.

C<sub>S(OFF)</sub> (OFF-state capacitance): the internal capacitance seen at an analog switch terminal when the switch is open or OFF.

**V**<sub>ct</sub> (crosstalk voltage): crosstalk between digital inputs and an analog switch terminal, at a specified input signal and load.

**Xtalk (crosstalk)**: crosstalk between different analog switch terminals, at a specified input signal and load.

f<sub>(-3dB)</sub> (-3 dB frequency response): bandwidth of an analog switch, at a specified input signal and load.

**THD (total harmonic distortion)**: total harmonic distortion of a signal due to an analog switch, at a specified input signal and load.

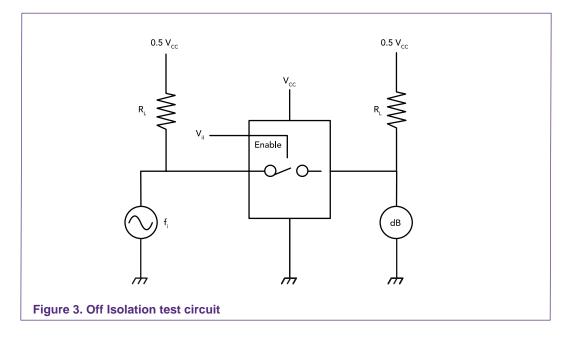

$\alpha_{iso}$  (isolation (OFF-state)): OFF-state isolation between terminals of a disabled analog switch, at a specified input voltage and load.

**Qinj (charge injection)**: charge injected from a digital control pin to the path of an analog switch, at a specified input voltage and load.

**Charge Injection:** As the switch turns ON or OFF, small amounts of charge can be injected from digital control signal in the path of analog control signals. It can also be seen as enable to output cross talk i.e. changing the state on control pin causes a charge to be coupled on the channel of transistor introducing signal noise.

**Total Harmonic Distortion:** When a signal passes through a non-ideal, non-linear device, additional content is added at the harmonics of the original frequencies. THD is a measurement of the extent of that distortion. Mathematically, THD can be defined as the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency.

Lesser THD allows the components in a loudspeaker, amplifier or microphone or other equipment to produce a more accurate reproduction by reducing harmonics added by electronics and audio media. A THD rating < 1% is considered to be in high-fidelity and inaudible to the human ear.

# 4. AC switching parameters

**Δt/ΔV (input transition rise and fall rate)**: the rate at which the inputs are permitted to change from LOW to HIGH or HIGH to LOW.

$t_r$  (rise time): time taken for a signal to rise, usually measured from 10% to 90% of final level.

$t_{f}$  (fall Times): time taken for a signal to fall, usually measured from 90% to 10% of final level.

$t_{pd}$  (propagation delay): the time required for a transition of an input to produce a transition on an output, at a specified output load and V<sub>CC</sub>.

t<sub>PLH</sub> (LOW to HIGH propagation delay): the time required for a transition of an input to produce a LOW to HIGH transition on an output, at a specified output load and  $V_{CC}$ .

$t_{PHL}$  (HIGH to LOW propagation delay): the time required for a transition of an input to produce a HIGH to LOW transition on an output, at a specified output load and V<sub>CC</sub>.

$t_{TLH}$  (LOW to HIGH output transition time): the time required for an output signal to rise, usually measured from 10% to 90% of the final level.

t<sub>THL</sub> (HIGH to LOW output transition time): the time required for an output signal to fall, usually measured from 10% to 90% of the final level.

$t_W$  (pulse width): the time between the leading and trailing edges of a pulse, at specified levels and  $V_{\rm CC}$

$t_h$  (hold time): the interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which the data to be recognized must be maintained at the input in order to ensure continued recognition. A negative hold time indicates that the correct logic level may be released prior to the timing pulse and still be recognized.

$t_{su}$  (set-up time): the interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which the data to be recognized must be maintained at the input in order to ensure recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

$t_{\rm PHZ}$  (HIGH to OFF-state propagation delay): the time required for a transition of an input to produce a HIGH to OFF-state transition on an output, at a specified output load and  $V_{\rm CC}$ .

$t_{PLZ}$  (LOW to OFF-state propagation delay): the time required for a transition of an input to produce a LOW to OFF-state transition on an output, at a specified output load and  $V_{CC}$ .

\_\_\_\_\_

AN11733

$t_{PZH}$  (OFF-state to HIGH propagation delay): the time required for a transition of an input to produce an OFF-state to HIGH transition on an output, at a specified output load and  $V_{CC}$ .

$t_{PZL}$  (OFF-state to LOW propagation delay): the time required for a transition of an input to produce an OFF-state to LOW transition on an output, at a specified output load and  $V_{CC}$ .

$t_{en}$  (enable time): the time required for a transition of an input to produce an OFF-state to LOW transition or an OFF-state to HIGH transition on an output, at a specified output load and  $V_{CC}$ .

$t_{dis}$  (disable time): the time required for a transition of an input to produce a LOW to OFFstate transition or a HIGH to OFF-state on an output, at a specified output load and V<sub>CC</sub>.

**t**<sub>rec</sub> (recovery time): the time between the end of an overriding asynchronous input, typically a clear or reset input, and the earliest permissible beginning of a synchronous control input, typically a clock input.

$t_{sk(o)}$  (output skew time): the difference in propagation delay of outputs of a single device with all inputs switching simultaneously, under identical load conditions.

f; (input frequency): the frequency of a signal applied to an input.

fo (output frequency): the frequency of an output signal.

${\bf f}_{max}$  (maximum frequency): the maximum frequency of operation. Outputs should switch between 10% and 90% of V\_{CC}.

C<sub>i</sub> (input capacitance): the internal capacitance of an input pin.

**C**<sub>o</sub> (power dissipation capacitance): the internal capacitance of an output pin.

**C**<sub>pd</sub> (power dissipation capacitance): equivalent capacitance value of a device or channel of a device for calculating dynamic power dissipation.

# 5. Legal information

#### 5.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of noninfringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

### 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# 6. Contents

| 1.  | Electrical characteristics |    |

|-----|----------------------------|----|

| 1.1 | Currents                   |    |

| 1.2 | Voltages                   | 4  |

| 2.  | Typical data sheet view    |    |

| 3.  | Analog switches            | 6  |

| 4.  | AC switching parameters    | 8  |

| 5.  | Legal information          | 10 |

| 6.  | Contents                   | 11 |

|     |                            |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2015

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 15 October 2015 Document identifier: AN11733